### **Combinational Arithmetic Circuits**

### Addition:

- Half Adder (HA).

- Full Adder (FA).

- Carry Ripple Adders.

- Carry Look-Ahead Adders.

### • Subtraction:

- Half Subtractor.

- Full Subtractor.

- Borrow Ripple Subtractors.

- Subtraction using adders.

### • Multiplication:

Combinational Array Multipliers.

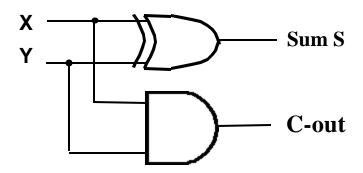

### Half Adder

- Adding two single-bit binary values, X, Y produces a sum S bit and a carry out C-out bit.

- This operation is called half addition and the circuit to realize it is called a half adder.

### **Half Adder Truth Table**

| Iı | Inputs |   | tputs |

|----|--------|---|-------|

| X  | Y      | S | C-out |

| 0  | 0      | 0 | 0     |

| 0  | 1      | 1 | 0     |

| 1  | 0      | 1 | 0     |

| 1  | 1      | 0 | 1     |

$$S(X,Y) = S(1,2)$$

$S = X'Y + XY'$

$S = X A Y$

C-out(x, y, C-in) =

$$\mathbf{S}$$

(3)

C-out =  $\mathbf{X}\mathbf{Y}$

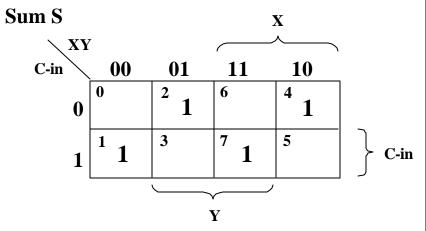

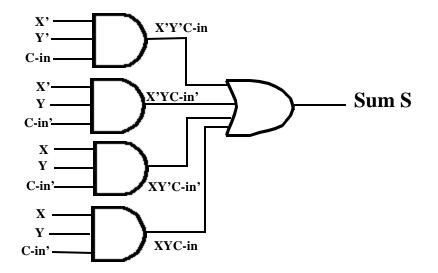

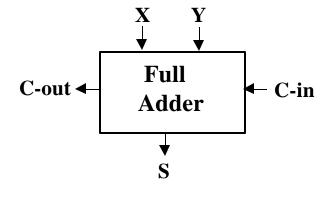

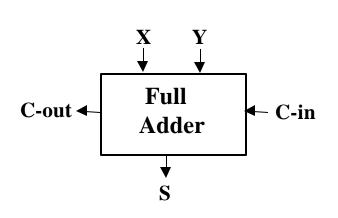

### **Full Adder**

Adding two single-bit binary values, X,

Y with a carry input bit C-in produces

a sum bit S and a carry out C-out bit.

### **Full Adder Truth Table**

| Inputs |   |      | Outputs |       |  |

|--------|---|------|---------|-------|--|

| X      | Y | C-in | S       | C-out |  |

| 0      | 0 | 0    | 0       | 0     |  |

| 0      | 0 | 1    | 1       | 0     |  |

| 0      | 1 | 0    | 1       | 0     |  |

| 0      | 1 | 1    | 0       | 1     |  |

| 1      | 0 | 0    | 1       | 0     |  |

| 1      | 0 | 1    | 0       | 1     |  |

| 1      | 1 | 0    | 0       | 1     |  |

| 1      | 1 | 1    | 1       | 1     |  |

$$S(X,Y, C-in) = S(1,2,4,7)$$

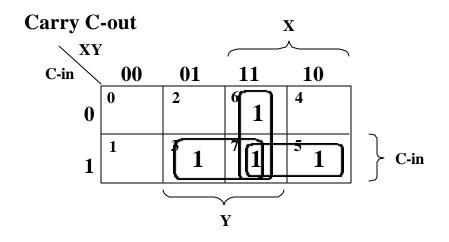

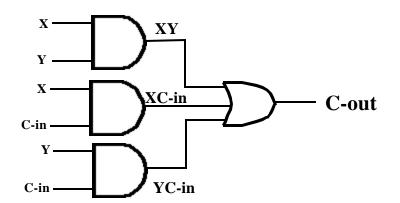

C-out(x, y, C-in) =  $S(3,5,6,7)$

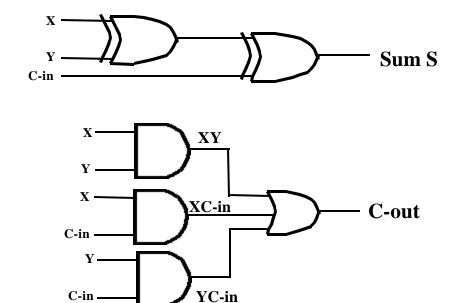

$$\begin{split} S &= X'Y'(C\text{-in}) + XY'(C\text{-in})' + XY'(C\text{-in})' + XY(C\text{-in}) \\ S &= X \ \oplus \ Y \ \oplus \ (C\text{-in}) \end{split}$$

C-out = XY + X(C-in) + Y(C-in)

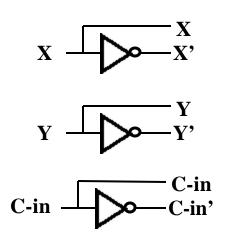

# Full Adder Circuit Using AND-OR

# Full Adder Circuit Using XOR

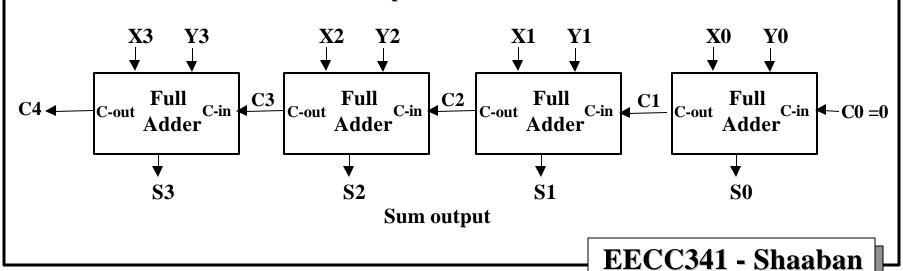

# n-bit Carry Ripple Adders

- An n-bit adder used to add two n-bit binary numbers can built by connecting in series n full adders.

- Each full adder represents a bit position j (from 0 to n-1).

- Each carry out C-out from a full adder at position j is connected to the carry in C-in of the full adder at the higher position j+1.

- The output of a full adder at position j is given by:

$$S_{j} = X_{j} X_{j} X_{j} C_{j}$$

$$C_{j+1} = X_{j} Y_{j} X_{j} C_{j} + Y C_{j}$$

- In the expression of the sum  $C_j$  must be generated by the full adder at the lower position j-1.

- The propagation delay in each full adder to produce the carry is equal to two gate delays  $= 2 \mathbf{D}$

- Since the generation of the sum requires the propagation of the carry from the lowest position to the highest position, the total propagation delay of the adder is approximately:

Total Propagation delay  $= 2 n \mathbf{D}$

# 4-bit Carry Ripple Adder

Adds two 4-bit numbers:

X = X3 X2 X1 X0

Y = Y3 Y2 Y1 Y0

producing the sum S = S3 S2 S1 S0, C-out = C4 from the most significant position j=3

**Sum Output**

Inputs to be added

Total Propagation delay  $= 2 n\mathbf{D} = 8\mathbf{D}$

or 8 gate delays

Data inputs to be added

#7 Lec # 11 Winter 2001 1-16-2002

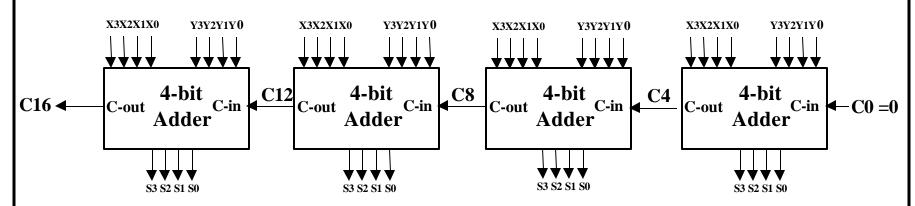

# Larger Adders

- Example: 16-bit adder using 4, 4-bit adders

- Adds two 16-bit inputs X (bits X0 to X15), Y (bits Y0 to Y15) producing a 16-bit Sum S (bits S0 to S15) and a carry out C16 from most significant position.

Data inputs to be added X (X0 to X15), Y (Y0-Y15)

Sum output S (S0 to S15)

Propagation delay for 16-bit adder =  $4 \times propagation delay of 4-bit adder$ =  $4 \times 2 \text{ n} \mathbf{D} = \mathbf{4} \times 8 \mathbf{D} = 32 \mathbf{D}$ or 32 gate delays

# **Carry Look-Ahead Adders**

- The disadvantage of the ripple carry adder is that the propagation delay of adder (2 n**D**) increases as the size of the adder, n is increased due to the carry ripple through all the full adders.

- Carry look-ahead adders use a different method to create the needed carry bits for each full adder with a lower constant delay equal to three gate delays.

- The carry out C-out from the full adder at position i  $\ensuremath{C_{j+1}}$  is given by:

C-out =

$$C_{i+1} = X_i \cdot Y_i + (X_i + Y_i) \cdot C_i$$

- By defining:

- $G_i = X_i \cdot Y_i$  as the carry generate function for position i (one gate delay) (If  $G_i = 1$  C  $_{i+1}$  will be generated regardless of the value  $C_i$ )

- $-P_{i}=X_{i}+Y_{i} \ as \ the carry propagate function for position i \qquad (one gate delay)$  (If  $P_{i}=1$   $C_{i}$  will be propagated to  $C_{i+1}$ )

- By using the carry generate function  $G_i$  and carry propagate function  $P_i$ , then  $C_{i+1}$  can be written as:

$$C-out = C_{i+1} = G_i + P_i \cdot C_i$$

• To eliminate carry ripple the term  $C_i$  is recursively expanded and by multiplying out, we obtain a 2-level AND-OR expression for each  $C_{i+1}$

# Carry Look-Ahead Adders

• For a 4-bit carry look-ahead adder the expanded expressions for all carry bits are given by:

$$C_{1} = G_{0} + P_{0}.C_{0}$$

$$C_{2} = G_{1} + P_{1}.C_{1} = G_{1} + P_{1}.G_{0} + P_{1}.P_{0}.C_{0}$$

$$C_{3} = G_{2} + P_{2}.G_{1} + P_{2}.P_{1}.G_{0} + P_{2}.P_{1}.P_{0}.C_{0}$$

$$C_{4} = G_{3} + P_{3}.G_{2} + P_{3}.P_{2}.G_{1} + P_{3}.P_{2}.P_{1}.G_{0} + P_{3}.P_{2}.P_{1}.P_{0}.C_{0}$$

where

$$G_i = X_i \cdot Y_i$$

$P_i = X_i + Y_i$

- The additional circuits needed to realize the expressions are usually referred to as the carry look-ahead logic.

- Using carry-ahead logic all carry bits are available after three gate delays regardless of the size of the adder.

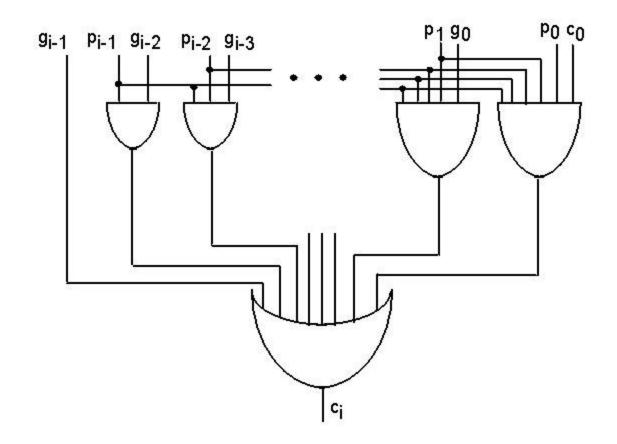

# **Carry Look-Ahead Circuit**

$$C_{i} = G_{i-1} + P_{i-1} G_{i-2} + ... + P_{i-1} P_{i-2} ... P_{1} G_{0} + P_{i-1} P_{i-2} ... P_{0} C_{0}$$

# **Binary Arithmetic Operations Subtraction**

- Two binary numbers are subtracted by subtracting each pair of bits together with borrowing, where needed.

- Subtraction Example:

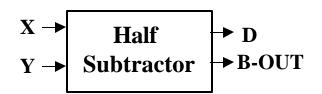

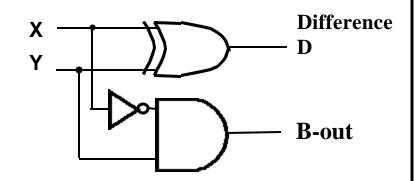

### **Half Subtractor**

- Subtracting a single-bit binary value Y from anther X (I.e. X -Y) produces a difference bit D and a borrow out bit B-out.

- This operation is called half subtraction and the circuit to realize it is called a half subtractor.

#### **Half Subtractor Truth Table**

| In | nputs        | Outputs |              |  |  |

|----|--------------|---------|--------------|--|--|

| X  | $\mathbf{Y}$ | D       | <b>B-out</b> |  |  |

| 0  | 0            | 0       | 0            |  |  |

| 0  | 1            | 1       | 1            |  |  |

| 1  | 0            | 1       | 0            |  |  |

| 1  | 1            | 0       | 0            |  |  |

$$D(X,Y) = S(1,2)$$

$D = X'Y + XY'$

$D = X A Y$

B-out(x, y, C-in) =

$$\mathbf{S}$$

(1)

B-out =  $\mathbf{X}$ 'Y

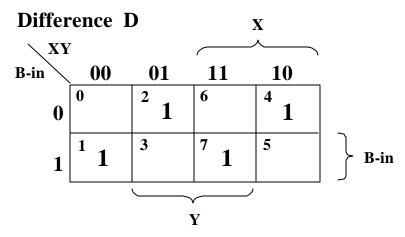

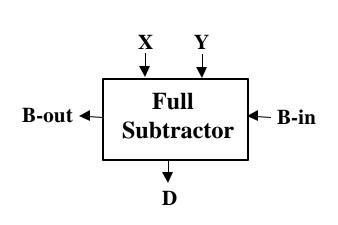

### **Full Subtractor**

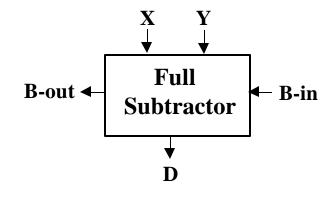

• Subtracting two single-bit binary values, Y, B-in from a single-bit value X produces a difference bit D and a borrow out B-out bit. This is called full subtraction.

#### **Full Subtractor Truth Table**

| Inputs   | Outputs |

|----------|---------|

| <u> </u> |         |

| X | Y | B-in | D | <b>B-out</b> |

|---|---|------|---|--------------|

| 0 | 0 | 0    | 0 | 0            |

| 0 | 0 | 1    | 1 | 1            |

| 0 | 1 | 0    | 1 | 1            |

| 0 | 1 | 1    | 0 | 1            |

| 1 | 0 | 0    | 1 | 0            |

| 1 | 0 | 1    | 0 | 0            |

| 1 | 1 | 0    | 0 | 0            |

| 1 | 1 | 1    | 1 | 1            |

|   |   |      | 1 |              |

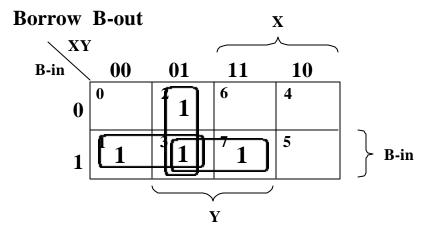

$$S(X,Y, C-in) = S(1,2,4,7)$$

C-out(x, y, C-in) =  $S(1,2,3,7)$

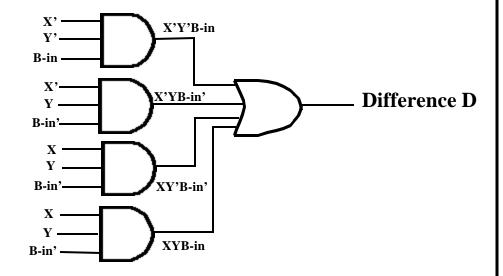

$$S = X'Y'(B-in) + XY'(B-in)' + XY'(B-in)' + XY(B-in)$$

$S = X \oplus Y \oplus (C-in)$

$$\mathbf{B}\text{-out} = \mathbf{X'Y} + \mathbf{X'}(\mathbf{B}\text{-in}) + \mathbf{Y}(\mathbf{B}\text{-in})$$

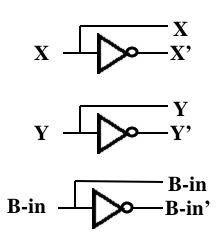

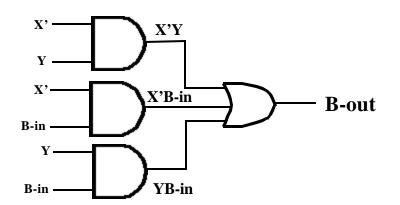

# Full Subtractor Circuit Using AND-OR

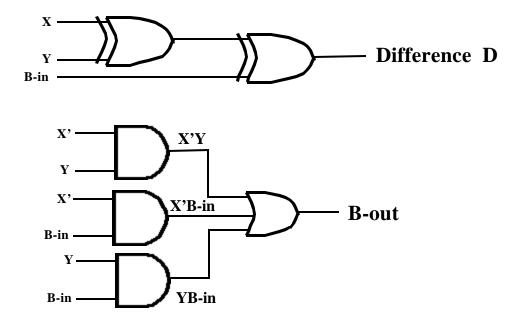

# Full Subtractor Circuit Using XOR

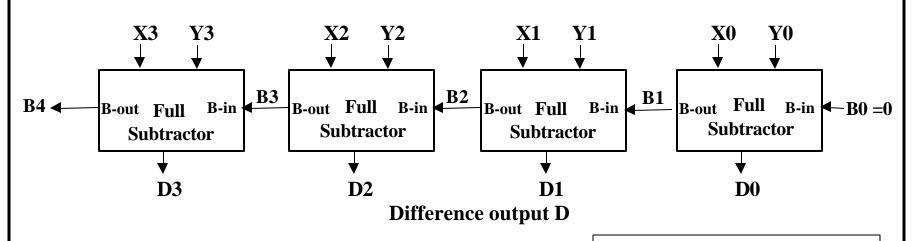

### n-bit Subtractors

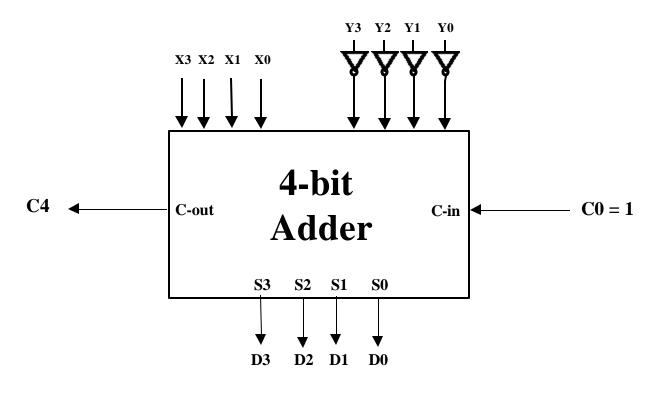

An n-bit subtracor used to subtract an n-bit number Y from another n-bit number X (i.e X-Y) can be built in one of two ways:

- By using n full subtractors and connecting them in series, creating a borrow ripple subtractor:

- Each borrow out B-out from a full subtractor at position j is connected to the borrow in B-in of the full subtracor at the higher position j+1.

- By using an n-bit adder and n inverters:

- Find two's complement of Y by:

- Inverting all the bits of Y using the n inverters.

- Adding 1 by setting the carry in of the least significant position to 1

- The original subtraction (X Y) now becomes an addition of X to two's complement of Y using the n-bit adder.

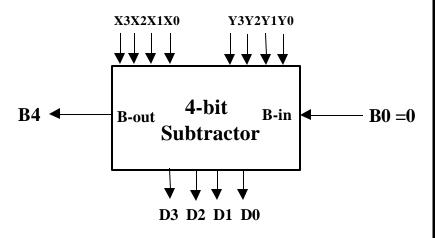

# 4-bit Borrow Ripple Subtractor

#### **Inputs**

**Subtracts two 4-bit numbers:**

$$Y = Y3 Y2 Y1 Y0 from$$

$$X = X3 X2 X1 X0$$

$$Y = Y3 Y2 Y1 Y0$$

producing the difference D = D3 D2 D1 D0,

B-out = B4 from the most significant

position j=3

**Difference Output D**

#### Data inputs to be subtracted

#18 Lec # 11 Winter 2001 1-16-2002

# 4-bit Subtractor Using 4-bit Adder

#### **Inputs to be subtracted**

**Difference Output**

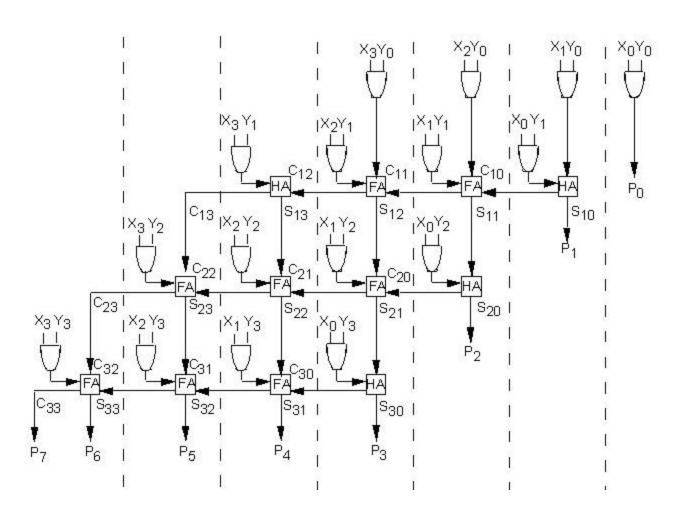

# **Binary Multiplication**

- Multiplication is achieved by adding a list of shifted multiplicands according to the digits of the multiplier.

- Ex. (unsigned)

| 11   | 1011         | . 1 | multiplicar | nd (4 bits)     | )     |       | X3    | X2 X1 | X0    |

|------|--------------|-----|-------------|-----------------|-------|-------|-------|-------|-------|

| X 13 | X 1101       |     | multiplier  | <b>(4 bits)</b> |       | X     | Y3    | Y2 Y1 | Y0    |

|      |              |     |             |                 |       | X3.Y0 | X2.Y0 | X1.Y0 | X0.Y0 |

| 33   | 1011         |     |             |                 | X3.Y1 | X2.Y1 | X1.Y1 | X0.Y1 |       |

| 11   | $0\ 0\ 0\ 0$ |     |             | X3.Y2           | X2.Y2 | X1.Y2 | X0.Y2 |       |       |

|      | 1011         |     | X3.Y3       | X2.Y3           | X1.Y3 | X0.Y3 |       |       |       |

| 143  | 1011         | P7  | P6          | P5              | P4    | P3    | P2    | P1    | P0    |

|      |              |     |             |                 |       |       |       |       |       |

|      | 10001111     |     | Product     | (8 bits)        |       |       |       |       |       |

- An n-bit X n-bit multiplier can be realized in combinational circuitry by using an array of n-1 n-bit adders where is adder is shifted by one position.

- For each adder one input is the multiplied by 0 or 1 (using AND gates) depending on the multiplier bit, the other input is n partial product bits.

# 4x4 Array Multiplier